韩国存储器两大巨头海力士与三星,将在2026年2月15日至19日于旧金山举行的国际固态电路大会(ISSCC 2026)上,同台亮出各自的下一代LPDDR6存储器解决方案。

图片来源:推特

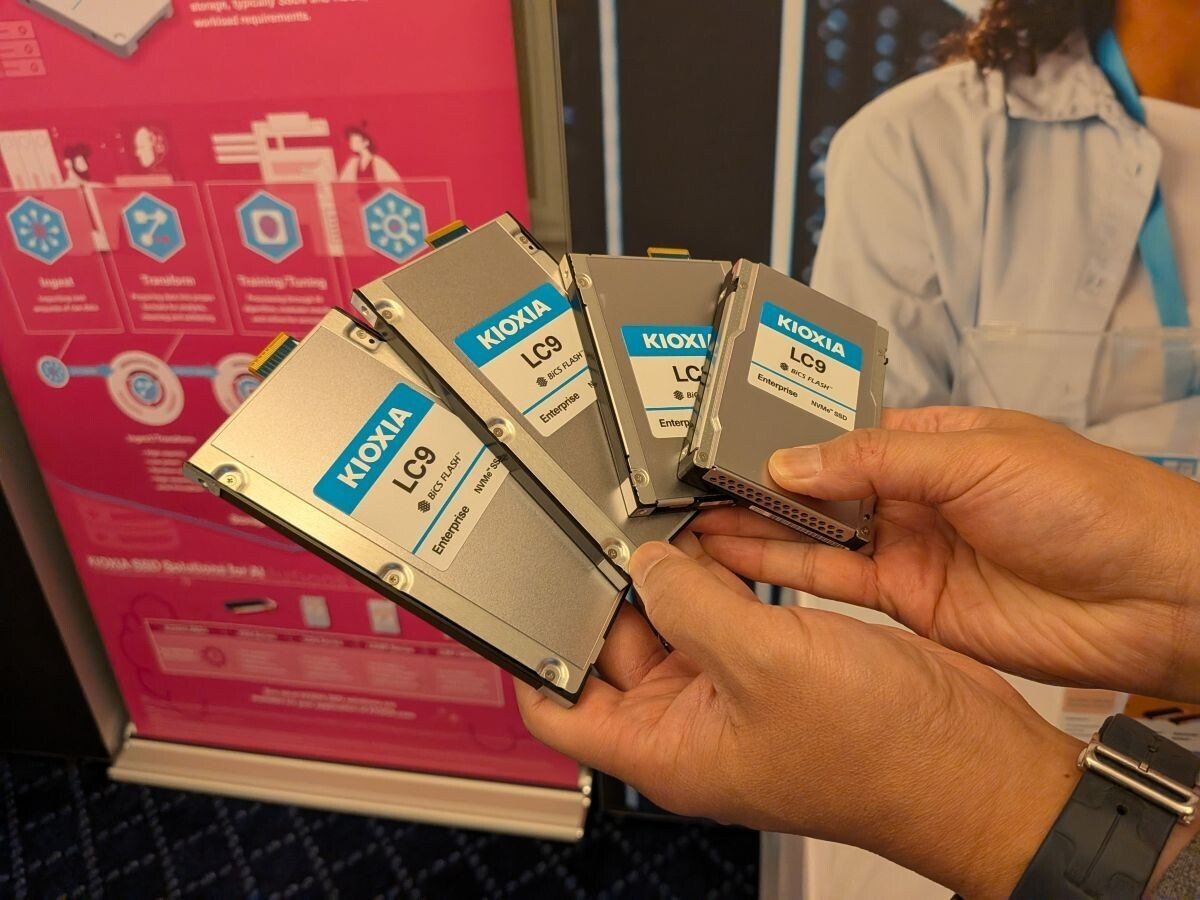

海力士将推出容量为16Gb的LPDDR6模块,每引脚传输速率达到14.4Gbps,实力不容小觑。该产品基于1c代(1γ代)半导体节点打造,正是海力士旗下的第六代10纳米级DRAM工艺。海力士明确表示,这些新模块将运行在JEDEC规定的LPDDR6最高速率水平,意味着该公司已接近这个技术标准的上限,也暗示了未来可能会推出超频版本的LPDDR6X产品。

图片来源:推特

三星则在此前CES 2026首次展示的基础上,对LPDDR6规格进行了提升。其 16Gb LPDDR6 模块的运行速率从几周前公布的10.7Gbps提升至12.8Gbps,这一速度提升可以说是相当明显。据行业消息,三星的LPDDR6采用12纳米工艺制造,三星表示,与前代LPDDR5X相比,新一代 LPDDR6 在能效方面实现了21%的提升。

在接口技术层面,三星的LPDDR6内存采用NRZ信号进行输入输出,还专门配备了12DQ子通道,而行业内普遍猜测,海力士的同系列模块大概率也会采用类似设计,毕竟这种方案在实用性上确实颇具优势。

图片来源:推特

除了基础规格的提升,两家公司展示的LPDDR6产品,还涵盖了新一代标准引入的多项技术更新。其中最重要的变化之一,就是首次在DRAM标准中引入了集成行激活计数追踪机制。可能有朋友会疑惑,这一机制到底有什么用?简单来说,它通过控制器与内存芯片共同监控行激活次数,以直接应对Row Hammer攻击,而不再像以往那样仅依赖基于刷新机制的缓解方式。通过在控制器与芯片两端协同监测激活计数,这一设计提升了对潜在攻击的防护能力。

图片来源:推特

LPDDR6标准还创新性地将元数据嵌入数据包内部,不再通过专用引脚进行传输。这一改变让内存系统实现了更全面的片内与链路级纠错能力,可支持单比特纠错与多比特检测,与此前标准相比,这种设计在数据完整性保障方面,无疑是向前迈出了一大步。

最后,咱们再来聊聊大家都很关心的功耗问题。LPDDR6支持跨三条电压轨的动态电压频率调节,而前代的LPDDR5仅支持两条电压轨,新增的电压轨设计,能够更好地适配不同场景下的功耗需求。同时,新标准还引入了效率模式,既能有效降低I/O功耗,又能实现设备密度翻倍,一举两得。

图片来源:推特

整体来看,海力士与三星此次在ISSCC 2026上的同台亮相,两者将分别展示基于最新工艺节点打造的16Gb LPDDR6产品,分别达到14.4Gbps与12.8Gbps的每引脚速率,同时围绕新一代标准,在行激活计数追踪、嵌入式元数据纠错机制以及三电压轨动态调节等多个关键技术领域,全面展示各自的技术进展,这场同台竞技,必将成为本次ISSCC 2026的一大看点。

图片来源:推特